Sparq-2020 System on Chip (SoC)

-

First in the Market

-

5G 3GPP standard compliant (Rel-15)

-

Includes 5G PHY and MAC ( Layers 1 , 2)

-

Optimized for URLLC – including “Sparq Minislots“ and integrated mobile edge computing (“I-MEC”)

-

FPGA based (16 nm technology)

-

Enables customization via API’s

-

Main features:

-

3 x 200 MHz BW

-

> 10 Gbps Capacity (with carrier aggregation)

-

Latency < 0.5 msec

-

MU-MIMO; Beam Forming, CoM

-

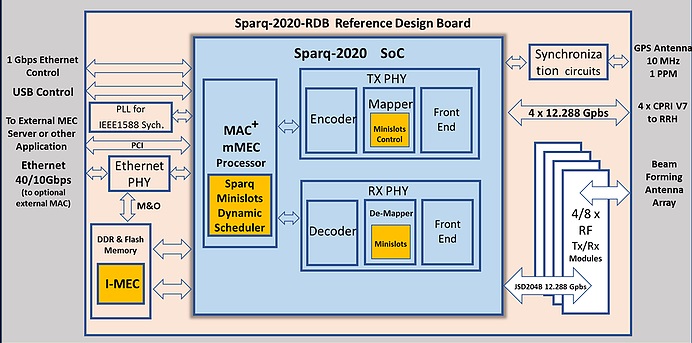

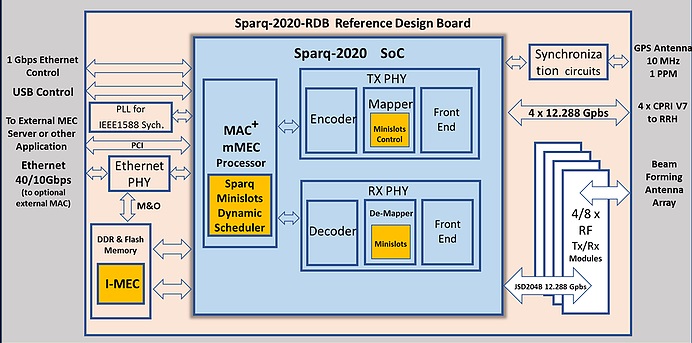

Sparq-2020-RDB (Reference Design Board)

Sparq-2020 Reference Design Board block diagram

Main Features

- Provides an easy and painless process from design to commercial product

- Supports different products within the 5G architecture ( New Radio, RRH, SRRH, etc.)

- Supports different frequencies by external RF boards interfaces

- Large FPGA including 4 ARM cores

- 72bits DDR4 SODIMM 4G connected to ARM cores

- 64 bits DDR4 to FPGA Logic

- Embedded GPS receiver

- Battery option to GPS receiver, save RTC when power is off

- Programmer clocks chip, support IEEE 1588 synchronization

Interfaces

- FMC connector

- 4 x 10G SFP+

- 4 x CPRI SFP+ (can be used for Ethernet 10G instead)

- 1 x USB to control 4 UARTS: a- for CPU, b-for CPU, c- for FPGA, d- for GPS

- 2 x Mictor connectors for debugging

- 5 x SMA connectors: a- External 10MHz input, b- External 10MHz output, c- 1pps input, d- 1pps output, e- GPS Antenna

- Additional clock generator chip - Ultra Low-Noise JESD204B Compliant Clock Jitter

- PCIe x 4 Gen2 for external server connection or MEC

Power and Environmental

- Power Inputs: -48V/24V/12 V

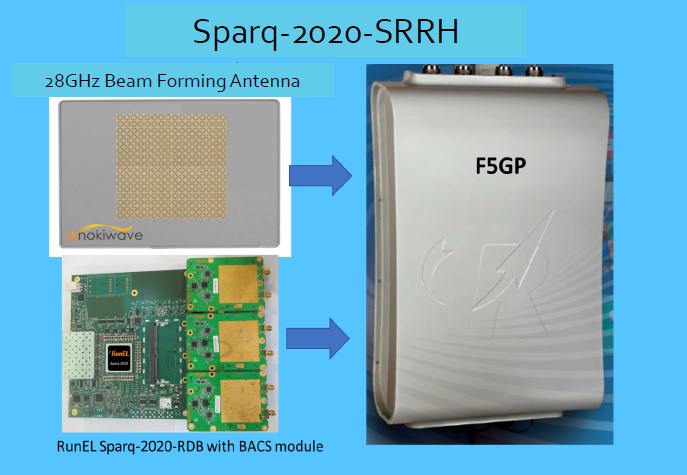

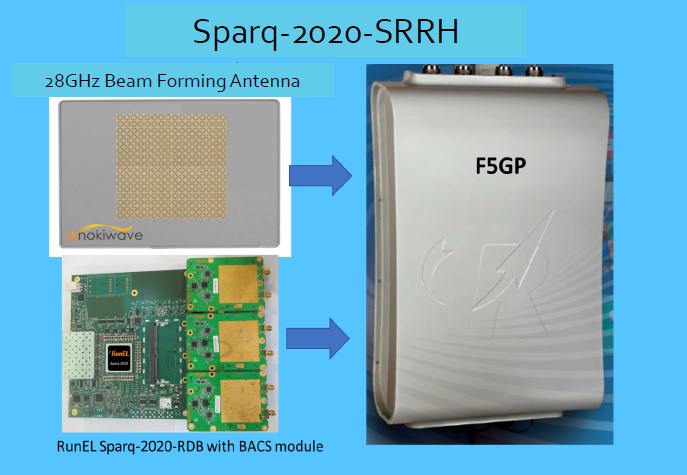

Sparq-2020 SRRH

Sparq-2020 SRRH

Sparq-2020 Reference Design Board block diagram